| Posted By

GreatWhiteRetro

on 2025-10-25

15:55:46

|  WDC65C02 apparently not using $0000-0001 on 8501 Adapter WDC65C02 apparently not using $0000-0001 on 8501 Adapter

[NOTE: My original question seems to be answered, and this thread is devolving into unrelated things. The WDC part isn't reserving $0000-0001 for anything special, and there might be an entirely different cause of the I/O pins not working. Me wanting to use a WDC 65C02 on a TED machine is a curiosity, nothing more.]

[Original content follows]

Both SukkoPera and I have recently tried using dmantione's 6502 to 8501 adapter daughterboard:

https://www.freepascal.org/~daniel/8501/

... on a LittleSixteen v4 system. A MOS 6502 I scavenged from a 1541 board seems to work as expected, but a WDC part, while successfully booting to BASIC and passing CPU tests on Diag264, doesn't seem to be generating any I/O on the P0 through P7 pins on the adapter.

My first attempt involved using a David Murray-inspired workaround that he used to make a WDC part work on a VIC 20 CR / Short board. This involved lifting pin 1 and tying some other WDC-specific input pins high using a pullup resistor. SukkoPera went further and disconnected or tied other pins high that could have interfered, and he also used better logic parts than the ones PCBway used on the daughterboards they made for me.

Both attempts got the same result - the system can POST and seemingly pass CPU tests but there was no noticeable activity on P0-P7. Both the Diag264 manual I/O tests and my scope showed no activity at all on the general I/O pins.

I wondered if the WDC part reserved addresses $0000-0001 for something. I would have expected a 'normal' 6502-based computer, something like Ben Eater's 6502 project, to have some RAM there considering this is zero-page space or possibly stack space. The daughterboard has two custom registers mapped there instead, using a GAL and glue logic to emulate the P0-P7 pins. Is that something the WDC part can't normally allow, or have we missed something?

|

|

Posted By

gerliczer

on 2025-10-23

03:16:01

|  Re: WDC65C02 apparently not using $0000-0001 on 8501 Adapter Re: WDC65C02 apparently not using $0000-0001 on 8501 Adapter

So, you are saying that the WDC denies to perform any bus access to the lowest two addresses? Wild.

|

|

Posted By

Crown

on 2025-10-23

06:05:34

|  Re: WDC65C02 apparently not using $0000-0001 on 8501 Adapter Re: WDC65C02 apparently not using $0000-0001 on 8501 Adapter

Do you actually have the right data on A0-15, and D0-D7, coming out of the CPU when writing to $00 and $01?

I would bet that the GAL and glue logic emulating the port is not compatible with the WDC65C02 timing requirement or wiring.

But even if you make it work, there are multiple differences, which can break compatibility on a general level. All illegal opcodes are removed, there are additional instructions, and various 6502 features considered as bugs are changed/"fixed", increment instruction behaviour is changed, which all can trigger compatibility problems

|

|

Posted By

GreatWhiteRetro

on 2025-10-23

09:16:57

|  Re: WDC65C02 apparently not using $0000-0001 on 8501 Adapter Re: WDC65C02 apparently not using $0000-0001 on 8501 Adapter

The point of trying to use the WDC part is to replace all legacy parts with modern versions, no old-stock. We finally have a TED replacement in FPGA form and we have ACIA and SID replacements, we’re just missing the CPU.

Part of the testing is to see what software fails with the WDC part, if any. Unsupported op codes are supposed to be just that - unsupported. I just want to get the I/O working and then I can test a bunch of software.

|

|

Posted By

gerliczer

on 2025-10-23

11:51:02

|  Re: WDC65C02 apparently not using $0000-0001 on 8501 Adapter Re: WDC65C02 apparently not using $0000-0001 on 8501 Adapter

Why not making an FPGA 8501 instead? Similar things are already done. I remember reading about some open 6502 core. Then there was the 65F100 project, too.

|

|

Posted By

SukkoPera

on 2025-10-23

12:17:51

|  Re: WDC65C02 apparently not using $0000-0001 on 8501 Adapter Re: WDC65C02 apparently not using $0000-0001 on 8501 Adapter

I am strongly convinced that, in order to achieve the best compatibility, any CPU recreation should limit itself to the bare minimum required. Since 6502 CPUs are easily obtainable, I don't see any point into reimplementing the full CPU, with the risk of introducing subtle timing bugs and incompatibilities. The maintenance effort would also increase considerably.

What I would do would be a minimum implementation of just the 8501 I/O port and bus tristating, but that is exactly what the MOS CPU Replacer and Daniel Mantione's "8501 Equivalent" projects already do. And they even manage to do so using only standard 74xx logic (and a GAL for the latter), which is even better, in particular since I am totally unable to write Verilog or VHDL code.

We are trying to use a 65C02 mostly for curiosity (myself) or for the sake of using entirely new parts (GWR). It's working pretty well as far as I can say, except that the I/O port is not collaborating, I will investigate ASAP.

|

|

Posted By

Crown

on 2025-10-23

13:47:32

|  Re: WDC65C02 apparently not using $0000-0001 on 8501 Adapter Re: WDC65C02 apparently not using $0000-0001 on 8501 Adapter

The biggest compatibility problem with the WDC65C02 is the modified RMW behaviour, standard 6502 will do a read cycle, then a write back cycle with original values and finally a write cycle with the modified value. The WDC65C02 is replacing the middle write cycle with a read cycle. The RMW mechanism is widely used to acknowledge and clear all sorts of TED registers like the interrupt status register. Most recently I saw it used for clearing handshake bits on the TCBM interface in Bard's Tale I

|

|

Posted By

GreatWhiteRetro

on 2025-10-24

13:34:50

|  RMW vs RRW Cycles RMW vs RRW Cycles

Sounds like any adapter using the WDC part would need to emulate the original CPU's RMW cycle. Maybe it could cache the read and write it back out while the WDC part reads it back, but that sounds very complicated to do in logic.

For all I know this might even be the cause of the non-working P0-P7 pins.

|

|

Posted By

Litwr

on 2025-10-24

13:44:17

|  Re: WDC65C02 apparently not using $0000-0001 on 8501 Adapter Re: WDC65C02 apparently not using $0000-0001 on 8501 Adapter

A lot of +4 software can't work on the 65C02.

|

|

Posted By

SukkoPera

on 2025-10-25

04:51:24

|  Re: WDC65C02 apparently not using $0000-0001 on 8501 Adapter Re: WDC65C02 apparently not using $0000-0001 on 8501 Adapter

Can you guys provide a list of SW that you think will not work with the 65C02? Of course I expect issues with anything using illegal opcodes (but then again, can you point me to something that surely does use them?), but I'm quite optimistic for the rest. Let's see!

|

|

Posted By

gerliczer

on 2025-10-25

05:02:17

|  Re: WDC65C02 apparently not using $0000-0001 on 8501 Adapter Re: WDC65C02 apparently not using $0000-0001 on 8501 Adapter

Try any demos. Interrupts are usually acknowledged with an RMW instruction. Also, Crown mentioned two days ago Bard's Tale like such a programme.

|

|

Posted By

Lavina

on 2025-10-25

05:34:55

|  Re: WDC65C02 apparently not using $0000-0001 on 8501 Adapter Re: WDC65C02 apparently not using $0000-0001 on 8501 Adapter

My recent demos contain undocumented opcodes

|

|

Posted By

Litwr

on 2025-10-25

07:06:09

|  Re: WDC65C02 apparently not using $0000-0001 on 8501 Adapter Re: WDC65C02 apparently not using $0000-0001 on 8501 Adapter

IMHO using the 65C02 in the C+4 is a very strange idea. Can you imagine such a thing for the C64 or Atari? A more sensible option would be a detachable accelerator based on the high-frequency 65C02, like the SuperCPU. It would be interesting to combine NMOS and CMOS 6502s on a board that replaces the 7501/8501, allowing the 65C02 to use quadruple frequency. I remember there being a popular board like this for the Amiga. It was placed in place of the CPU and contained two CPUs, the removed 68000 and the 80286.

|

|

Posted By

GreatWhiteRetro

on 2025-10-25

12:52:55

|  Example: VIC 2020 and Mini-PET Example: VIC 2020 and Mini-PET

@Litwr I haven't seen a WDC part on a 64 or Atari 8-bit, but I've seen emulation support for the 65816 on the Altira emulator for Atari 8-bit, and I've seen a real WDC 65C02 implemented on TFW8B's Mini-PET and VIC 2020 projects. These also appear to use WDC versions of the 6522 VIA I/O chips.

https://github.com/danwerner21/vic2020

https://www.tfw8b.com/product/minipet-40-80-standalone-computer-kit/

This does seem like a can of worms I've opened up. But if nothing else, my initial guess is incorrect then - the WDC part isn't reserving $0000-0001 for anything special.

The VIC 2020 and Mini-PET systems are examples of what I'd like to see for the TED architecture someday. The Mini-PET already uses a microcontroller for video, and the VIC 2020 could use Vicenary's FPGA VIC implementation. We have FPGATED, VIC-II Kawari, and other replacements.

While I think emulating RMW on a WDC part might be difficult, I don't believe it's impossible or impractical, at least not yet. Might involve emulating the Modify part as writing to the bus and allowing reading from the CPU to satisfy TED register resets, I don't know yet.

|

|

Posted By

gerliczer

on 2025-10-25

13:49:07

|  Re: WDC65C02 apparently not using $0000-0001 on 8501 Adapter Re: WDC65C02 apparently not using $0000-0001 on 8501 Adapter

Accepting an FPGA implementation of the TED but rejecting such a thing when talking about the CPU seems somewhat self-contradicting to me.

|

|

Posted By

GreatWhiteRetro

on 2025-10-25

15:51:07

|  Re: WDC65C02 apparently not using $0000-0001 on 8501 Adapter Re: WDC65C02 apparently not using $0000-0001 on 8501 Adapter

@gerliczer I could just go whole-FPGA and use a project like this one:

https://github.com/ishe/plus4

My understanding is this is an entire plus/4 on the same FPGA core that FPGATED was done on. It would certainly be a lot less expensive than building a LittleSixteen, but probably not as fun.

Even considering using a modern FPGA brings up the same criticism David Murray made about the Mini-PET, where the microcontroller used for video could likely emulate the PET almost entirely.

I'll try to find Daniel and ask him about the WDC part on his adapter, but unless there's a comparably simple fix or only a little redesign needed, I don't need to chase this down too much.

|

|

Posted By

SukkoPera

on 2025-10-26

04:20:29

|  Re: WDC65C02 apparently not using $0000-0001 on 8501 Adapter Re: WDC65C02 apparently not using $0000-0001 on 8501 Adapter

@gerliczer: it makes perfect sense to me, the 8501 is just a 6502 with a few extra features and 6502s are easily available and a dime a dozen, so why reimplement the full thing? On the other hand, there is nothing like a "partial TED" with just a few missing features, so it necessarily has to be reimplemented completely.

I don't also see why using a 65C02 on a +4 would be strange: it is a rather compatible 6502 CPU, so it is definitely worth a try, at least to define precisely to what extent it works. I definitely won't do anything more than trying to get the thing working with Daniel's adapter, and in this regard I think I've already found the issue, but not the root cause yet.

And yes, the FPGA on the FPGATED could definitely implement the whole +4, but then we would have a sort of C16Ultimate, which is personally not what I want. But maybe the new Commodore has already contacted Istvan for that, who knows...

|

|

Posted By

gerliczer

on 2025-10-26

04:20:30

|  Re: WDC65C02 apparently not using $0000-0001 on 8501 Adapter Re: WDC65C02 apparently not using $0000-0001 on 8501 Adapter

@GreatWhiteRetro Yes, you could. But why would you? You want to build a piece of hardware that is mostly equivalent to an original machine. Which is a cool project.  That needs the exact same individual LSI components the original needed. You could go for original TED and CPU, as those still can be obtained. (Yes, it is getting harder and harder, gets more and more expensive, but still doable.) You chose to settle for replacing the TED with a compatible FPGA implementation. Yet, you are insisting on replacing the CPU with an incompatible LSI device. That needs the exact same individual LSI components the original needed. You could go for original TED and CPU, as those still can be obtained. (Yes, it is getting harder and harder, gets more and more expensive, but still doable.) You chose to settle for replacing the TED with a compatible FPGA implementation. Yet, you are insisting on replacing the CPU with an incompatible LSI device.

I met this argument about FPGA and microcontroller based emulations are being the same unacceptable things numerous time and I think it is a misconception. A software emulation running on a μC or a CPU is "bending" an underlying alien hardware architecture to output data that generates some approximation of the original hardware's output. An FPGA software, however, is an abstract description of how to connect elementary logic elements and, on occasions, some additional higher level hardware blocks like PLLs or multipliers into a logic network that will approximate the basic signals generated in the original LSI device. E.g. calculating the screen content into a frame buffer that will be somehow displayed strongly differs from generating the Luma/Chroma signals that you must transmit to a display device.

|

|

Posted By

SukkoPera

on 2025-10-27

18:53:52

|  Re: WDC65C02 apparently not using $0000-0001 on 8501 Adapter Re: WDC65C02 apparently not using $0000-0001 on 8501 Adapter

Root cause found and problem fixed, IEC devices now seem to work reliably on 65C02.

Did a few quick tests, what works:

- Giana

- Outrun

- Digiloi

What doesn't:

- False Idols (resets early during loading, need to test with normal 6502)

- Lykia (has graphical glitches during introduction, game menu has wrong colors and disappears at some point, music keeps playing).

- Pets Rescue (doesn't load)

Will disclose root cause in a few days, need to borrow a tool to make a better analysis.

UPDATE 27/10:

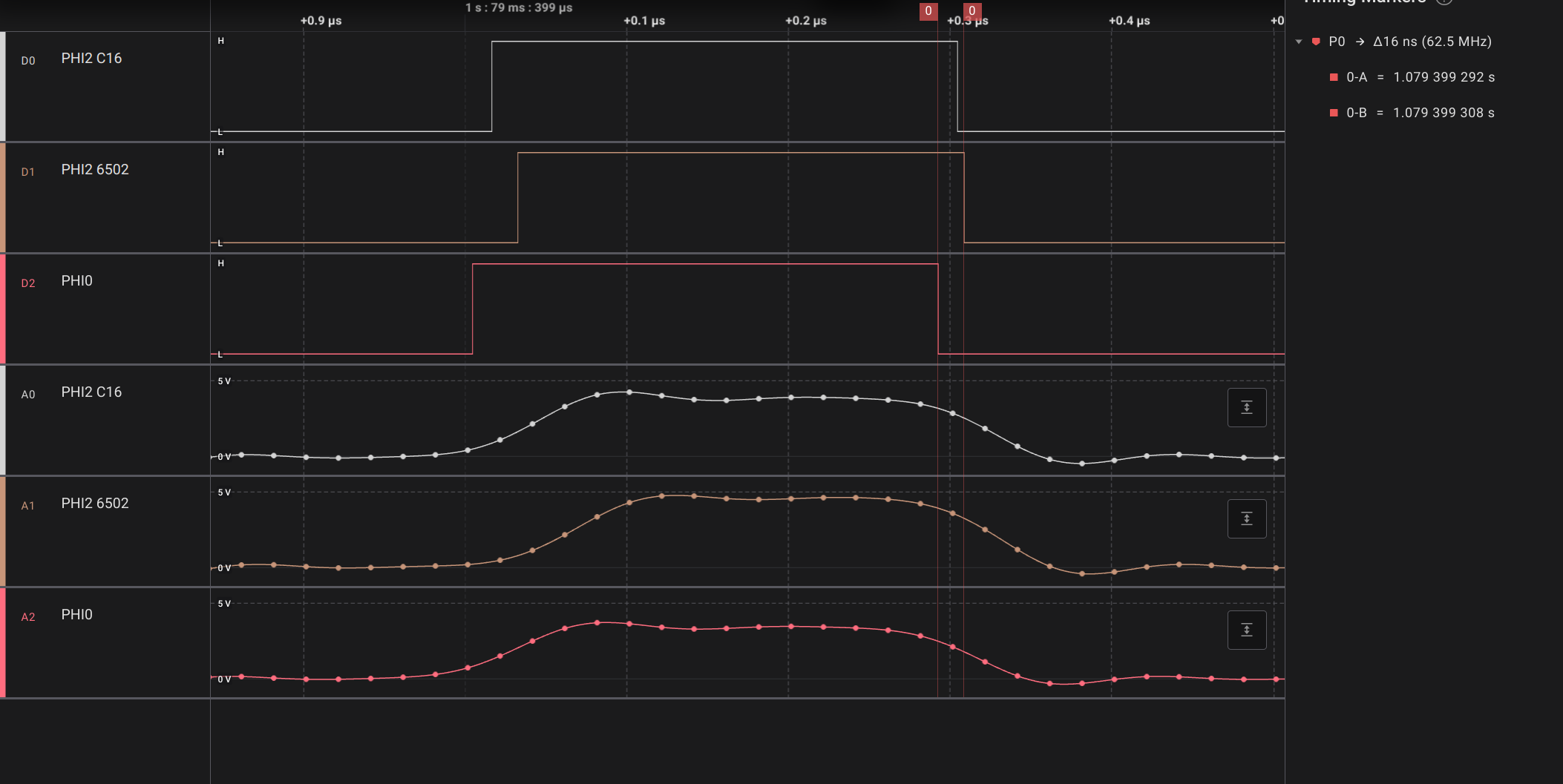

So, this is the cause of the problem, 6502:

On the 264 series, the falling edge of PHI2 marks addresses valid. This signal is normally generated by 6502 CPUs as a slightly altered version of PHI0, the main clock signal. Although, with the 8501 they ran out of pins (compared to the 6510, they removed PHI2 and /NMI to introduce GATE_IN and an extra I/O pin) so they resorted to synthesizing a similar signal through the PLA.

The GAL on Daniel's 6502 adapter needs PHI2 in order to know when the CPU is accessing $0000/$0001 in order to drive the logic that is implementing the corresponding registers. Although, since the "official" PHI2 signal does not reach the 8501 socket, the GAL is using the PHI2 signal generated by the 6502. As you can see from the above image, while the two signals are not exactly the same, the falling edge of one more or less matches that of the other. In particular, the falling edge of both PHI2 signals always comes after the falling edge of PHI0. The GAL relies on the short interval between the two in order to generate the pulse that latches the data bus value into the register at $0001 (called PORTLATCH in the GAL equations).

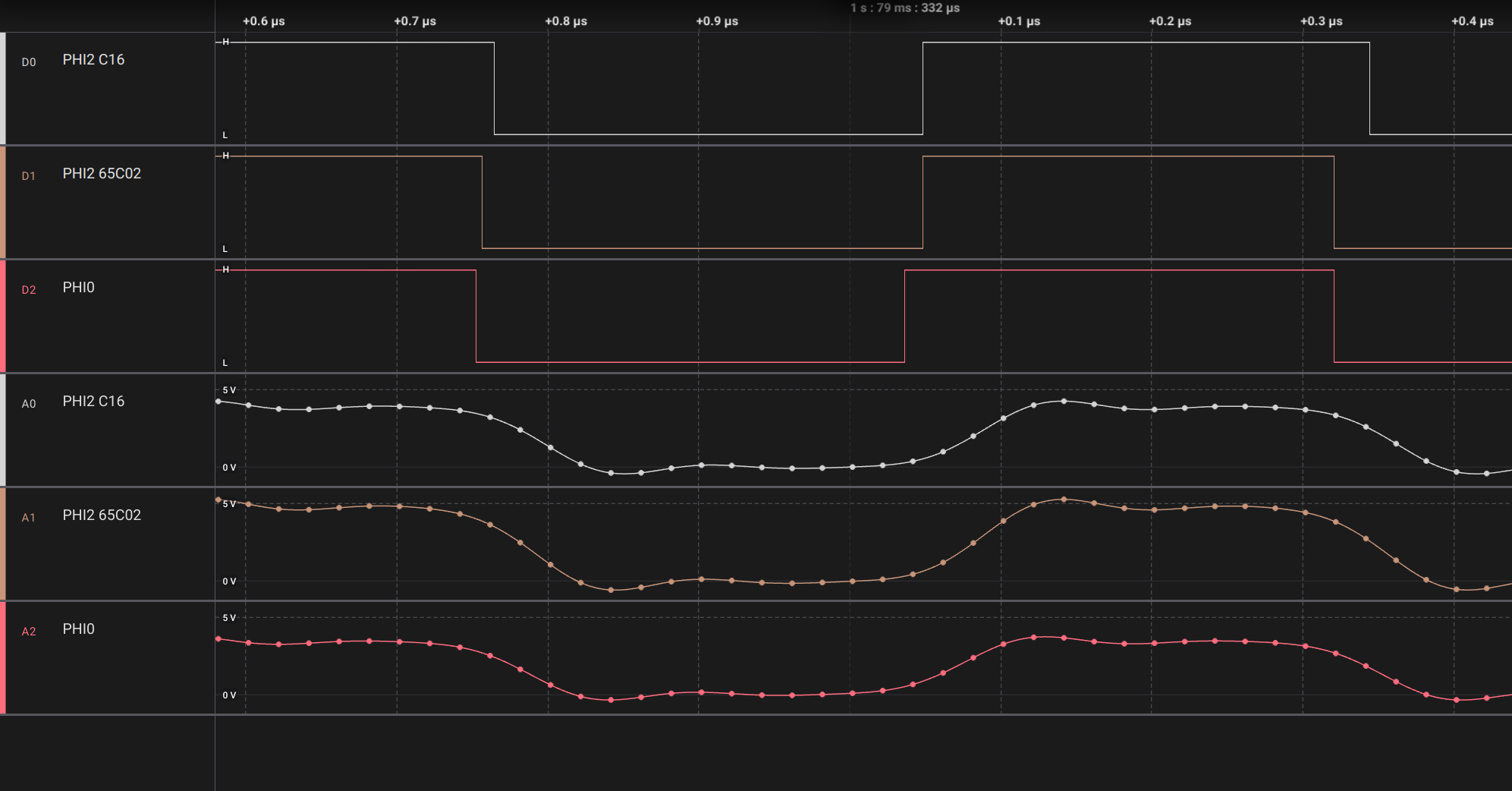

Unfortunately, the above does not always happen with the 65C02:

As you can see, the falling edge of the PHI2 generated by the CPU comes well in advance compared to the one generated by the system. It is too close to the falling edge of PHI0, sometimes it even comes sooner, so the PORTLATCH signal is not generated correctly and the value is not stored in the $0001 register.

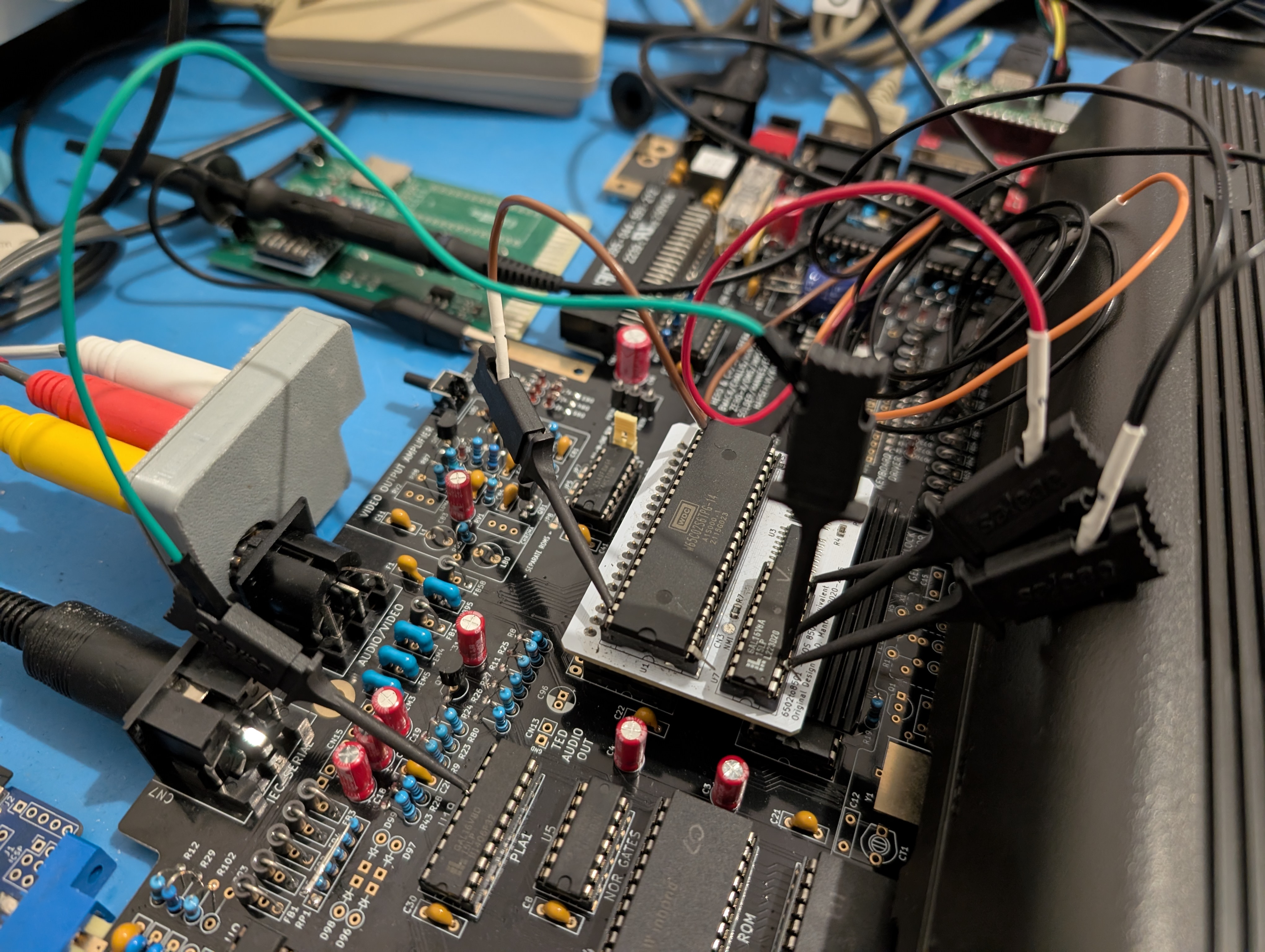

The solution is to drive the GAL with the system PHI2 signal: lift pin 3 so that it stays out of the socket and connect it to pin 17 of the PLA (or pin 14 of U19 on L16 V4).

1 1 |

|

Posted By

GreatWhiteRetro

on 2025-10-27

20:29:26

|  And this is why I’m no Adrian Black And this is why I’m no Adrian Black

@SukkoPerra this is one excellent troubleshooting job!

This by itself won’t solve all of the problems, but it at least enables exploration of them.

If I read this right, I need to replace the CPU’s Clock2 output with the one the TED PLA or GAL PLA generates.

|

|

Posted By

SukkoPera

on 2025-10-28

04:16:27

|  Re: WDC65C02 apparently not using $0000-0001 on 8501 Adapter Re: WDC65C02 apparently not using $0000-0001 on 8501 Adapter

Yes but it's easier to do it at the GAL input, it's the only thing that uses PHI2 on the adapter anyway.

This is what I did (green wire, disregard analyzer wires):

1 1 |

|

| |

Copyright © Plus/4 World Team, 2001-2025. Support Plus/4 World on Patreon |